안녕하세요 일이입니다!!

오늘도 재미없는 이론공부를 시작해볼까요?ㅠㅠㅋ

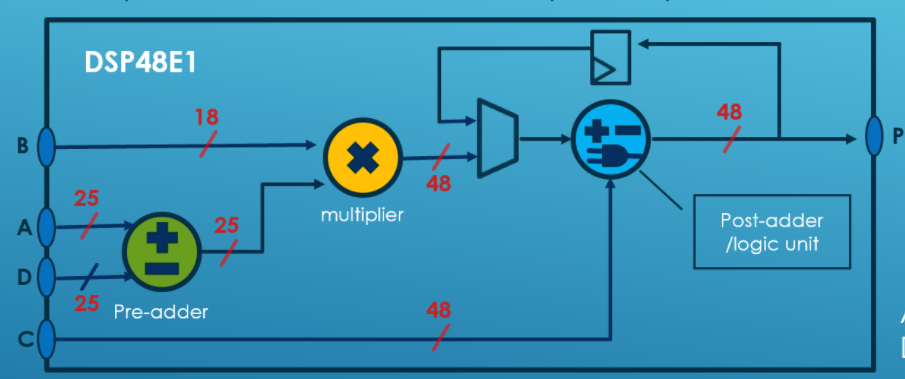

DSP48E1s : 중간에서 긴 산술 단어의 길이를 가진 신호에 고속 산술 구현을 위한 전문 조각.

DSP48E1s는 위 그림처럼 로직 단위가 있는 Pre-adder/subtractor, multiplier 및 Post-adder/subtractor로 구성됩니다.

멀티플렉싱 회로를 사용하여 레지스터의 유연한 사용을 허용하고 계산의 동적 변경을 지원합니다.

(즉, 필요에 따라 사이클 별로 기능을 변경할 수 있음.)

입력에 A, B, C, D로 라벨이 표시되고 출력은 P로 표시됩니다.

이 장치는 P=(A+D)*B, P=P'+C 또는 그 밖의 많은 기능을 계산할 수 있다.

또한, 각각 24비트 또는 12비트의 짧은 추가/감산/누적 작동을 구현하여 SIMD 처리를 할 수 있다.

추가로 Post-adder는 논리 단위로서의 추가 기능을 가지고 있다.

DSP48E1s를 결합하여 복잡한 계산을 수행할 수 있으며, 단어 길이도 부동 소수점 산술 구현에 적합하다.

저전력 소비의 장점과 함께 계산적으로 까다로운 산술 회로를 구현하는데 매력적입니다.

Zynq의 일반 IOB(Input/Output Facility)를 집합적으로 선택이라고 합니다.

I/O 리소스 및 이러한 리소스는 각각 50 IOB의 뱅크로 구성되며, IOB에는 단일 입력 또는 출력 신호에 대해 외부 세계에 물리적인 연결을 제공하는 하나의 패드가 포함되어 있다.

I/O 뱅크는 고성능(HP) 또는 HR(High Range)로 분류되며, 이는 다양한 I/O 표준과 전압을 지원한다.

HP 인터페이스는 1.8V의 전압으로 제한되며 일반적으로 메모리 및 기타 칩에 대한 고속 인터페이스에 사용되는 반면, HR 인터페이스는 최대 3.3V의 전압을 허용하고 A/O를 공급한다.

다양한 IO 표준 단일 엔드 신호 전송과 차동 신호 전송이 모두 지원되며, 연결당 1 IOB 및 2 IOB가 필요하다.

고도로 지정된 Zynq 장치에는 로직 패브릭에 내장된 GTX 트랜스시버, 고속 통신 인터페이스 블록이 포함됩니다.

(PCI Express, Serial Rapid를 비롯한 전용 인터페이스IO, SCSI 및 SATA)

PCI Express를 구현하려면 GTX 트랜스시버 자체 외에도 두 번째 하드 IP 블록과 블록 RAM이 필요합니다.

GTX 송수신기는 '쿼드'로 구현됩니다.

즉, 각각 해당 채널, 송신기 및 수신기에 대한 전용 PLL(Phase Locked Loop)로 구성됩니다.

Zynq 장치와 패키지 쇼센에 따라 최대 12.5Gbps의 속도가 지원됩니다.

이 인터페이스는 네트워킹 장비, 하드 디스크 및 추가 FPGA 또는 Zynq 장치와 같은 독립적인 외부 장치에 대한 연결을 만드는 데 사용될 수 있습니다.

GTX 블록과의 작업 측면에서,

원하는 인터페이스에 대한 코어를 자동으로 생성하는 마법사 도구를 통해 지원이 제공됩니다.

사용자 관점에서, 이것은 시스템에 블록을 도입하고, 원하는 프로토콜과 하드웨어 옵션을 선택하고,

파라미터를 설정하는 것을 포함한다.

디지털 변환에 대한 아날로그 - PL에는 XADC 블록이라는 또 다른 하드 IP 구성 요소가 포함되어 있습니다.

이것은 디지털 컨버터(ADC) 혼합 신호 하드웨어에 대한 아날로그 전용 세트로, 두 개의 별도의 12비트 ADC가 모두 1Msps에서 외부 아날로그 입력 신호를 샘플링할 수 있다. XADC 제어는 PS 내에 위치한 PS-XADC 인터페이스 블록을

이용하여 이루어지며, PS-XADC 제어 블록은 APU에서 실행되는 소프트웨어에서 자체적으로 프로그래밍할 수 있습니다. XADC 및 관련 리소스에 대한 확장 정보는 [18]에서 확인할 수 있습니다.

클럭 - PL은 PS로부터 4개의 개별 클럭 입력을 수신하며, PS와는 독립적으로 자체 클럭 신호를 생성 및 분배할 수 있는 기능을 추가로 갖추고 있습니다. 독립적 PL 자원은 7 시리즈 FPGA의 자원과 동일합니다.

프로그래밍 및 디버그 - PL 섹션에 JTAG 포트 집합이 제공. 일반적으로 배치 시 보다 안전한 방법이 선호되지만,

개발 단계에서는 JTAG 구성이 종종 사용됩니다. JTAG 지원 디버깅을 통해 제공되는 설비는 ARM 및 Xilinx 도구를 모두 사용하여 제공됩니다.

앞 절에서 언급했듯이, Zynq의 매력은 단지 그것의 구성 요소인 PS와 PL의 지지에 있는 것이 아니라, 완전한 통합 시스템을 형성하기 위해 그것들을 사용하는 능력에 있습니다. 이 점에서 핵심적 인에이블러는 두 부분 사이의 브리지를 형성하는 고도로 지정된 AXI 상호 연결과 인터페이스의 집합입니다. PS와 PL, 특히 EMIO 간에는 몇 가지 다른 유형의 연결도 있습니다. 이 절에서는 PS와 PL의 연결을 살펴보고 이 연결을 사용할 수 있는 방법을 고려합니다. 우리는 이러한 연결의 대부분이 바탕이 되는 AXI 표준을 도입하는 것으로 시작합니다.

다음에는 AXI를 자세하게 정리해보도록 하겠습니다!

'Engineering > ZYNQ' 카테고리의 다른 글

| [ZYNQ] 징크 공부하기 #3. 디바이스 징크 두번째 (0) | 2019.08.17 |

|---|---|

| [ZYNQ] 징크 공부하기 #2. 디바이스 징크 첫번째 (0) | 2019.08.10 |

| [ZYNQ] 징크 공부하기#1. 소개 (0) | 2019.08.03 |