안녕하세요 일이입니다!

오늘은 징크에 대해 좀 더 자세하게 알아볼까 합니다.

이전에 언급한 것처럼 ZYNQ는 PS(processing System)과 PL(Programmable Logic) 이렇게

2개의 섹션으로 구성되어 있습니다.

이 섹션들의 구조와 인터페이스를 알아보도록 하겠습니다.

모든 Zynq 장치의 기본적인 Processing System(PS)은 A dual-core ARM Cortex-A9 Processor를 포함하고 있다.

ARM processor는 Hard Processor로 대안으로 PL에 Xilinx MicroBlaze, Soft Processor가 존재한다.

일반적인 소프트 프로세서의 장점은 인스턴스의 수와 정확한 구현이 가능하다는 점이다.

하드 프로세서의 장점은 상당히 고성능이라는 점이다.

MicroBlaze 인스턴스는 시스템 내에서 특정 낮은 수준의 기능을 조정하는 역할을 가질 수 있다.

(주 ARM Processor에서 벗어나 전반적인 성능을 향상)

* 컴퓨터를 전공하신 분들은 아시겠지만 저처럼 비전공자라 모르는 분들을 위해서 인스턴스라는 용어를

간단하게 설명하고 넘어가도록 할게요~

인스턴스는 같은 클래스에 속하는 개개의 객체로, 하나의 클래스에서 생성된 객체를 말한다.

즉 클래스가 구체화되어, 클래스에서 정의된 속성과 성질을 가진 실제적인 객체로 표현된 것을 의미한다.

이때 추상적인 개념인 클래스에서 실제 객체를 생성하는 것을 인스턴스화(instantiation)라고 한다.

(이해되시나요? 저도 실은 명확하게 이해는 못한 부분이랍니다. ㅠㅠ

클래스와 객체에 대해서 명확하게 공부할 필요를 느끼네요. ㅠㅠ)

징크 시스템 내에서 PS에서 중요한 부분인 APU에 대해서 알아보도록 하겠습니다.

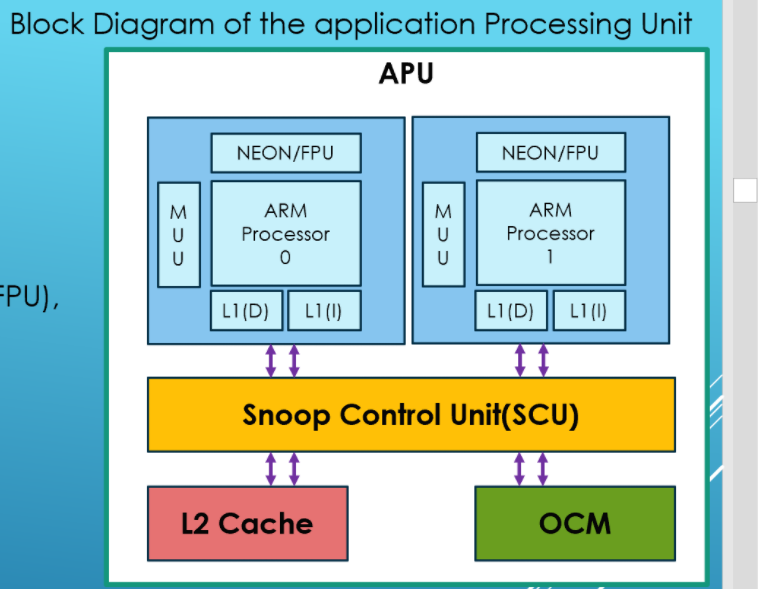

1. Application Processing Unit(APU)

APU(Application Processing Unit)

: 주로 두 개의 ARM 처리 코어로 구성되어 있으며, 각각은 관련된 연산 단위를 가지고 있다.

(MIPS : 1초당 100만 개의 단위의 명령어 연산을 하는 프로세스의 처리속도)

즉, NEON 미디어 처리 엔진(MPE)과 플로팅 포인트 유닛 (FPU), 메모리 관리 유닛(MMU) 및

레벨 1 캐시 메모리(지시를 위한 2개의 섹션과 데이터)로 구성됩니다.

또한 레벨 2 캐시 메모리와 OCM(On Chip Memory)가 포함되어 있습니다.

마지막으로 스눕 컨트롤 유닛(SCU)은 ARM 코어와 레벨 2 캐시 및 OCM 메모리 사이의 브리지를 형성합니다.

각 부분에 대해서 자세하게 알아볼까요?

-. 기본적으로 사용되는 ARM 처리 코어인 ARM Cortex-A9은 최대 1Ghz로 동작할 수 있습니다.

-. 두 코어는 각각 데이터와 지시를 위한 별도의 레벨 1 캐시를 가지고 있으며, 두 캐시는 모두 32KB이며,

자주 필요한 데이터와 빠른 액세스 시간과 최적의 프로세서 성능을 위한 지침을 로컬로 저장할 수 있습니다.

-. 두 코어는 지침과 데이터를 위해 512KB의 더 큰 레벨 2 캐시를 추가로 공유하며 APU에는

256KB의 온 칩 메모리가 더 있다.

-. MMU의 주요 역할은 가상 주소와 물리적 주소 사이를 변환하는 것입니다.

(TMI)

&. ARM 아키텍처는 임베디드 기기에 많이 사용되는 RISC 프로세서입니다.

(RISC(reduced instruction set computer) : CPU 안의 명령어를 최소로 줄여 단순하게 만든 프로세서.)

&. 마이크로프로세서 내부에 포함된 캐시를 온칩(on-chip) 캐시 또는 레벨 1캐시 칩 외부의 캐시를

오프 칩(off-chip) 캐시 또는 레벨 2 캐시라고 부릅니다.

엑세스 속도 : 레벨 1캐시 > 레벨 2캐시 > 주기억장치

용량 : 레벨 2캐시 > 레벨 1캐시

-. 스눕 제어 장치(SCU)는 프로세스와 레벨 1과 2 캐시 메모리 사이의 인터페이스와 관련된 작업을 수행합니다.

('snoopping'은 캐시 일관성, 즉 공유 캐시 리소스 간의 데이터 일관성을 관리하기 위한 몇 가지 메커니즘 중 하나.)

-. SCU는 L1(D)로 표시된 프로세서 데이터 캐시 메모리와 공유 레벨 2 캐시 메모리 간의 메모리 일관성 유지를 담당.

또한 레벨 2 캐시에 대한 액세스를 시작하고 제어하며, 필요한 경우 두 코어의 요청을 중재합니다.

SCU는 가속기 정합성 포트(ACP)를 통해 PS와 PL 사이에서 발생하는 트랜잭션을 추가로 관리합니다.

트랜잭션 : 데이터베이스에서 데이터 처리의 한 단위.

데이터베이스 시스템에서 복구 및 병행 시행 시 처리되는 작업의 논리적 단위입니다.

(1)Atomicity(원자성) : 트랜잭션의 연산은 데이터베이스에 모두 반영이 되든지 아니면 전혀 반영되지 않아야 합니다.

(2)Consistency(일관성) : 트랜잭션이 그 실행을 성공적으로 완료하면 언제나 일관성 있는 데이터베이스 상태로

변해야 합니다.

(3)Isolation(독립성) : 둘 이상의 트랜잭션이 동시에 병행 실행되는 경우 어느 하나의 트랜잭션 실행 중에

다른 트랜잭션의 연산이 끼어들 수 없습니다.

(4)Durability(영속성, 지속성) : 성공적으로 완료된 트랜잭션의 결과는 영구적으로 반영되어야 합니다.

타이머와 인터럽트 컨트롤러는 APU에 위치한 추가적인 기능 블록 프로그래밍 관점에서 ARM 지침은 ARM 프로세서에 배포하기 위해 필요한 모든 구성 요소를 포함하는 Xilinx Software Development Kit(SDK)를 통해 제공됩니다.

컴파일러는 ARM 및 Thumb 명령 집합(16비트 또는 32비트)과 8비트 Java 바이트 코드(Java Virtual Machine에 사용됨)를 함께 지원합니다.

주 ARM 프로세서에 대한 추가 기능으로서, NEON 엔진은 미디어와 DSP 유형 알고리듬의 전략적 가속화를 가능하게

하는 단일 지침 다중 데이터(SIMD) 기능을 제공합니다.

2번째의 마지막으로 단일 지침 다중 데이터(SIMD)에 대해서 정리하고 마치도록 하겠습니다.

SIMD(Single Instruction Multiple Data) : 병렬 프로세서 중 한 종류로, 하나의 명령어로 여러 개의 값을 동시에 계산.

SIMD 용어에서 알 수 있듯이, NEON 엔진은 여러 입력 벡터 세트를 수용할 수 있으며, 이 때 동일한 작동이

동시에 수행되어 상응하는 출력 벡터 세트를 제공합니다.

이러한 계산 방식은 다수의 데이터 샘플(픽셀)에서 동시에 작동하는 영상 및 비디오 처리와 같은 어플리케이션과 FIR(Finite Impulse Response) 필터 및 FFT(Fast Fourier Transforms)와 같은 일반적인 신호 처리 기능에 적합합니다.

이상으로 2번째 징크에 대한 정리를 마무리할까 하는데요.

저도 영문판 책을 번역하면서 공부하는 단계라서 아직 쉽게 설명할 능력이 안되니 많이 아시는 분들은

많은 조언 부탁드립니다.

저처럼 이제 공부를 시작한 분들이라면 포기하지말고 꾸준히 함께 공부하도록 해요!

그럼 이만 마무리하겠습니다.

좋은 하루 되세요~

'Engineering > ZYNQ' 카테고리의 다른 글

| [ZYNQ]징크 공부하기 #3. 디바이스 징크 두번째 (1) | 2019.09.01 |

|---|---|

| [ZYNQ] 징크 공부하기 #3. 디바이스 징크 두번째 (0) | 2019.08.17 |

| [ZYNQ] 징크 공부하기#1. 소개 (0) | 2019.08.03 |